Saturday 27 October 2012

5.7.1 Gate Current, IG

5.7.1 Gate Current, IG

Based on the lucky electron model, electrons acquire enough energy from the electric field in the channel to surmount the SiSiO2 barrier. Once the required energy to surmount the barrier has been obtained the electrons are redirected towards the SiSiO2 interface by some from of phonon scattering [17, 21].

These electrons, which surmount the SiSiO2 barrier, are injected into the oxide causing gate current, IG [21].

5.8 Fixed Oxide charge (Qf, Nf)

Fixed Charge is a positive charge in the oxide layer less than 2nm from the SiSiO2 interface. This charge is not in electrical communication with underlying charge. It is also assumed to be unchanged by gate bias [22]. Typically, a value of 1.82x10 10 eV 1 cm 2 is representative for the interface charge found in ultrathin oxide silicon MOS devices.

5.7 Relationship between Gate Leakage Current and Interface States

5.7 Relationship between Gate Leakage Current and Interface States

Gate leakage current had not been a major concern in the past as the amount is small and

insignificant. However, it increases in integration density of the Integrated Circuits and reduction of size of the MOSFETs makes leakage current associated to the interface states to be significant [21].

Reduction in transistor size entails very important electric field in the transistor channel. This caused injection of hot carriers in the gate oxide and creates defects in the SiSiO2 interface (interface states). The defects I the SiSiO2 interface in turn cause leakage current in the gate [19, 21].

This gate current is responsible for the degradation in device operating characteristics with time. This “reliability” issue is of considerably importance as the lifetime of electronic parts has to be guaranteed [19, 21].

5.6.2 Depletion

5.6.2 Depletion

When the gate voltage, VG, is slightly more than zero, this causes a net negative charge at the surface of the semiconductor due to the depletion of holes from the region near the surface leaving behind uncompensated ionized acceptors [8]. The MOSFET is said to operate in the depletion mode.

Donor type interface states will be below EFS and will be filled with electrons and be neutral. Acceptor type interface states will be above EFS and be empty of electrons thus being neutral [18].

5.6.3 Inversion

When the gate voltage, VG, is further increased, the semiconductor surface is inverted from ptype to ntype. The MOSFET is said to operate in the Inversion mode [8].

Donor type interface states will be below EFS and will be filled with electrons and be neutral. Acceptor type interface states that are below EFS will be filled with electrons and become negatively charged. The acceptor type interface states that are above EFS will still be empty of electrons and remain neutral [18].

5.6 Changes in Occupancy and Charge State with Gate Bias

5.6 Changes in Occupancy and Charge State with Gate Bias

This section will illustrate the change in occupancy and charge state with different gate

bias voltage. For this section we apply a small DrainSource Voltage (VDS) of 0.1 volt

and ground the source terminal.

5.6.1 Accumulation

When the gate voltage, VG is less than zero, the MOSFET is said to operate in the

Accumulation mode. Holes are drawn to the SiSiO2 interface and no electron flows from

source to drain [8].

Donor type interface states that are above Fermi level of the silicon, EFS, will be empty of

electrons and become positively charged, while those that are below EFS will be filled

with electrons and be neutral [18].

Acceptor type interface states will be above EFS and be empty of electrons thus being

neutral [18]. Figure 5.3: Energyband diagram in a ptype semiconductor showing the charge

trapped in the interface states when the MOSFET gate bias is VG < 0 [18]

5.4 Location of interface traps

5.4 Location of interface traps

Interface states are located at the SiSiO2 layer which separates the gate contact from the

conducting channel, which is underneath the gate and between the source and drain region.

5.5 Energy distribution of the interface states

The net charge in the interface states is a function of the position of the Fermi level in the

bandgap[18].

The energy or band gap of silicon is 1.12 eV and generally, acceptor states exist in the

upper half of the bandgap and donor states exist in the lower half of the bandgap.

An acceptor type interface state is neutral if the Fermi level is below the state and

becomes negatively charged if the Fermi level is above the state [18].

A donor type interface state is neutral if the Fermi level is above the state and becomes

positively charged is the Fermi level is below the state [18].

5.3 Properties of interface states

5.3 Properties of interface states

Generally there are two types of interface states, the acceptor type and the donor type. An

acceptor type interface state is electrically neutral when it is empty and negatively charged when filled with an electron [16, 18].

A donor type interface state is electrically neutral when it is filled with electron and positively charged when empty [18].

Besides being donor or acceptor, a particular interface state is also characterized by

1) Its precise energy level in the bandgap (eg: eV from the valence band edge)

2) Its spatial location (eg: distance from the drain)

3) Its density (eg: number of states per cm 2 for discrete states)

In MOSFETs, these interface states are also caused by hot carrier impacting on the surface. Interface states are known to cause degradation in device parameters such astransconductance, carrier mobility and threshold voltage and generally reduce device reliability and lifetime [17, 18 and 19].

Chapter 5

Chapter 5

Interface States in MOSFETs

5.1 Introduction

The SiSiO2 interface is the only known interface that is good enough to enable operation of MOSFETs to industrial standards. Thus, the properties of silicon dioxide are fundamental to the success of silicon integrated circuit technologies [16].

5.2 Properties of SiSiO2 interface

Although the oxide is not a crystal, the silicon and oxygen atoms are packed in an orderly

manner, each silicon atom is bonded to four oxygen atoms and each oxygen atom is bonded to two silicon atoms [16].

As the average distance between the oxygen atoms is larger than the average distance between the silicon atoms in the silicon, this means that some of the interface atoms from the silicon will inevitably miss oxygen atoms to create SiO bonds. This is also known as dangling bond [16].

Atoms from the silicon that remain bonded only to three silicon atoms with the fourth bond unsaturated, represents interface defects. The energy levels associated with the fourth unsaturated bond of the trivalent silicon atoms do not appear in the conduction or the valance band, rather in the silicon energy band gap [16].

Electrons and holes that appear on these levels cannot move freely as there is a relatively large distance between the neighbouring interfacial trivalent silicon atoms (these levels are localized and isolated from each other) [16, 17].

As these levels can effectively trap the mobile electrons and holes (from the conduction and valence bands respectively), these are called interface states. Impurity atoms and groups (such as H, OH and N) can be bonded to the unsaturated bonds of the interfacial trivalent silicon atoms, which result in a shift of the corresponding energy levels into the conduction and valence band. Although this process effectively neutralizes the interface states, it is not possible to enforce such a saturation of all the interfacial trivalent atoms, which means that the density of the interface states can never be reduces to zero [17].

Friday 26 October 2012

4.4 Revised simulations

4.4 Revised simulations

We used the same devices use in chapter 3 (3.5 nm oxide and 2.2 nm oxide) with similar ambient conditions and performed the revised expressions for the operations and then compared the obtained results with that obtained through the simulations of physical alphapower law MOSFET model.

Studying the IDS vs. VGS curves, we find a good impact of the newly engaged trapped charges and depletion capacitance. For both of the specimens, the proposed model shows lower values at the initial points of the subthreshold region. In the initial region, physical alphapower law MOSFET model shows a quite constant rise in the values of drain current, where the proposed model shows a slightly curved rise in the values of drain current. This may be taken as an effect of the appearance of the newly introduced capacitances that are varied with the applied gate bias. These plots show that the subthreshold slope for proposed model shows a higher value (63.5 mV/decade) than the alphapower law MOSFET model (59.9 mV/decade) in case of 3.5 nm oxide. Similarly, revised model shows a higher value (62.4 mV/decade) in case of 2.2 nm devices than the previous model (59.4 mV/decade).

Al l the above IDS vs. VDS curves show a good adjustment with the calculated capacitance for the MOS devices model. As we have proceeded with the combination of the capacitances, we obtained a decrement by an order of 10 in the value of the total capacitance to that of the capacitance used in the alphapower law MOSFET model. All the plots here show same amount of decrement in drain current value than that of the alpha model.

4.3 Modification of the alphapower law model

4.3 Modification of the alphapower

law model

Our study of the physical alphapower law MOSFET Model includes a modification about MOS capacitance. In thesubthreshold region, the effects of depletion capacitanceand capacitance due to interface trapped charges are not included. As a consequence

revised model is presented with the employment of interface trapped charge capacitance(Cit) and depletion capacitance (Cd). The revised model includes the arrangement of capacitances in the following manner [15]:

Now it comes to a point of determining the different components of the total capacitance(C). Oxide capacitance is varied from the flatband capacitance (CFB) to the intrinsic value of the oxide capacitance (ei/tox). The flatband capacitance is a series combination of Debye capacitance (Cdebye) and insulator capacitance (Ci) [15]. It is assumed that the oxide capacitance (Cox) varies linearly with the application of the gate bias voltage (VGS). In our proposal we determine the gate to substrate voltage (VGS) or the gate bias from surface potentials (fs) by the following equation [14]:

Then we analyzed the interface trap distribution and measured its value to be equal to 65.771 nF (See Chapter 5 for detail). Thus we take interface trapped charge capacitance, Cit = 65.771 nF. Then following the capacitor arrangement of figure 4.2 we measured the

equivalent MOS capacitance (Cmos). The calculated value of the Cmos is then used in the expressions of the various expressions of physical alphapower law MOSFET model in places of Cox. And thus we obtained a quite remarkable deviation in the measured values of the drain current, IDS.

Our study of the physical alphapower law MOSFET Model includes a modification about MOS capacitance. In thesubthreshold region, the effects of depletion capacitanceand capacitance due to interface trapped charges are not included. As a consequence

revised model is presented with the employment of interface trapped charge capacitance(Cit) and depletion capacitance (Cd). The revised model includes the arrangement of capacitances in the following manner [15]:

Now it comes to a point of determining the different components of the total capacitance(C). Oxide capacitance is varied from the flatband capacitance (CFB) to the intrinsic value of the oxide capacitance (ei/tox). The flatband capacitance is a series combination of Debye capacitance (Cdebye) and insulator capacitance (Ci) [15]. It is assumed that the oxide capacitance (Cox) varies linearly with the application of the gate bias voltage (VGS). In our proposal we determine the gate to substrate voltage (VGS) or the gate bias from surface potentials (fs) by the following equation [14]:

Then we analyzed the interface trap distribution and measured its value to be equal to 65.771 nF (See Chapter 5 for detail). Thus we take interface trapped charge capacitance, Cit = 65.771 nF. Then following the capacitor arrangement of figure 4.2 we measured the

equivalent MOS capacitance (Cmos). The calculated value of the Cmos is then used in the expressions of the various expressions of physical alphapower law MOSFET model in places of Cox. And thus we obtained a quite remarkable deviation in the measured values of the drain current, IDS.

Chapter 4

Modification of The Physical AlphaPower Law MOSFET Model

4.1 Introduction

The modifications of the physical alphapower law MOSFET model was obvious due to the incorporation of the fast interface states in the model. Although, the model was quite right in its manners to determine the MOS characteristics, the interface capacitance

determines the current response in a quite realistic manner.

4.2 Interface trapped charges

A detailed study of the MOS interface states is presented in chapter 5 in the following. But for the convenience of our discussion we would like to have a bird’s eye view on it.

Generally, an interfacetrapped charge (also called fast interfacestate charge) exists at the oxidesemiconductor

interface. It is caused by the defects at the interface, which gives rise to charge “traps”; these can exchange mobile carriers with the semiconductor, acting as donors or acceptors [14]. The interface trapped charges are very negligible in effect in

case of strong inversion but if we consider the case of very thin gate oxides then we find the trapped charges playing a vital role in case of determining MOS capacitance.

The energy band diagram for a MOS structure at positive voltage is as follows:

From the above figure, we see the existence of interface trapped charges in the oxide region of the MOSFET. Usually in case of significantly thick gate oxides these charges are not of any significance in calculating the MOS capacitance. But, as we see, when the oxide thickness is very thin then these charges existing near to the edge of the oxide surface strongly take part during the application of electric field [5]. So, we see that

negligence about the existence of these charges is not quite always right to determine a better current response from a MOSFET operation.

3.4.2.4 IDS vs. VDS curve (VGS = 2 volt):

3.4.2.4 IDS vs. VDS curve (VGS = 2 volt):

As we see, from the mathematical representation of the alpha powerlaw MOSFET model, the active region current and the saturation region current in IDS vs. VDS curvesand the subthreshold region current and the active region current in the IDS vs. VGS curve are linearly proportional to the determined oxide capacitance of the respective devices. So, the amount of current decreases with the increase of oxide thickness as oxide capacitance is inversely proportional to the oxide thickness.Also, the amount of access of both the devices in the active region in case of IDS vs. VDS curves increase with the increment of applied gate bias voltages. Similarly, the increment of the gate voltage increases also increases the value of the output current IDS (See figure3.2, 3.3, 3.4 & 3.5).

3.4.3 Subthreshold slope

From the representation of the model, we find that, subthreshold current DS SUB I depends

exponentially on gate bias voltage VGS. However, VDS has little influence once VDS

exceeds a few q kT b = . Obviously, we find a linear behaviour in the subthreshold regime

from figure 3.1 when we plot IDS – VGS. The slope of this line (or more precisely the

reciprocal of the slope) is known as the subthreshold slope, S, which has typical value of

~70 mV/decade at room temperature for stateoftheart MOSFETs. This means that a

change in the input VGS of 70 mV will change the output IDS by an order of magnitude.

Clearly, the smaller the value of S, the better the transistor is as a switch. A small value

of S means a small change in the input bias can modulate the output current considerably.

It can be shown that S is expressed by

The elaborated expression gives us an idea of representing the electrical equivalent circuit

of the MOSFET in terms of capacitors. The expression in brackets in the above equation

is simply the capacitor divider ratio that tells what the fraction of the applied gate bias

appears at the Si – SiO2 interface as the surface potential. Ultimately it is the surface

potential that is responsible for modulating the barrier between the source and drain, and

therefore the drain current, IDS. Hence, S is a measure of the efficacy of the gate potential

in modulating IDS. From equation (3.17) we find that S is improved by reducing the gate

oxide thickness, which is reasonable because if the gate electrode is closer to the channel,

the gate control is obviously better. The value of S is higher for heavy channel doping

(which increases the depletion capacitance) or if the silicon – oxide interface has many

fast interface states. In our observations, we obtained the value of S to be 59.9

mV/decade for 3.5 nm devices and 59.4 mV/decade for 2.2 nm devices. So, we find that

the decrement of the oxide thickness results in a better responsive MOSFET as a switch.

3.4 Simulations

We have chosen two MOS devices of ultrathin oxides: 1) a 3.5 nm device and 2) a 2.2 nm

device. For both the devices we simulated the IVcharacteristics plots in all the three

operating regions. We considered the 3.5 nm device as the first sample and the 2.2 nm

device as the second sample. We ran the simulations on both the devices under a common

ambient temperature which is of the value T = 20 o C (293 K).

3.4.2 IDS vs. VDS curve:

In case of determining the nature of the IDS – VDS curves the gate to source voltage, VGS

was kept constant for a full operating range of drain to source voltage. We have taken

four distinct values of gate to source voltage for the determination of IDS – VDS curve.

These are: 0.8 volt, 1 volt, 1.5 volt & 2volt.

3.4.2.1 IDS vs. VDS curve (VGS = 0.8 volt):

Chapter 3

Chapter 3

The Physical AlphaPower Law MOSFET Model

3.1 Introduction

In 1999, the proposal of the physical alphapower law MOSFET model [8] eliminated the

drawbacks of the previously widely utilized alphapower law MOSFET model [9]. In this

regard, it included the helpful features of the low power transregional MOSFET model

[10]. The addition of the low power transregional model brings in the salient features of

operation in all the regions (subthreshold, triode and saturation). To mention that the low

power transregional model [10] was an advantageous choice for predicting performance

of future technology generations and in particular for analyzing on/off drain current

tradeoffs. Due to the complex drain current equations the involvement with the alphapower

law MOSFET model brought the physical alphapower law MOSFET model. This

model included these salient features: 1) extension into the subthreshold region of

operation, 2) the effects of vertical and lateral high field mobility degradation and

velocity saturation and 3) threshold rolloff.

3.2 Model Derivation

The physical alphapower law MOSFET model was derived by coupling the simple

empirical alphapower law MOSFET model [9] and the more complex physics based low

power transregional MOSFET model [10]. The derivation of the model started by

equating the saturation drain current of the alphapower law MOSFET model [9],

equation (3.1) and the low power transregional model [10], equation (3.2)

Where ID0 (3.5) is a modified drive current that includes an effective mobility dependence

on VGS. Neglecting the small weak inversion contribution and performing a three term

binomial expansion of the bulk charge terms in DS AT I , the low power transregional

model’s saturation drain current [10] was simplified as

Where, (W/L) is the channel widthtolengthratio, Cox is the oxide capacitance per unit

area, meff is the effective mobility. meff depends on the gate bias voltage (VGS) as the

influence of gate bias is dominant in the expression of meff. Rather we can say for a more

accurate expression that meff depends on the transverse field, which, in turn, depends on

all terminal voltages [11]. A general expression of meff is given as follows:

A feature of the physical alphapower law MOSFET model describes that dependence of

carrier velocity on VGS is jointly described by ID0, (3.3)(3.6), as well as a (3.10). This

yields improved accuracy of the model for VGS near VT compared to the original alphapower

law model [8] that describes carrier velocity as a function of VGS solely through a.Therefore,

the values of a calculated by the physical alphapower law model re slightly larger than the

measured a values of the original alphapower law model [8] for short channel MOSFETs.

For further insight into the a parameter, analyses of the long channel MOSFET with

negligible carrier velocity saturation (ECL >> VDD VT) and the short channel MOSFET

with severe carrier velocity saturation (ECL << VDD VT) are performed in the model. In

the long channel case, the saturation voltage (3.4) may be simplified by performing a two

term binomial expansion such that

2.3 Basic MOSFET Operation

2.3 Basic MOSFET Operation

In the MOSFET, an inversion layer at the semiconductoroxide interface acts as a

conducting channel. For example, in an nchannel MOSFET, the substrate is ptype

silicon and the inversion charge consists of electrons that form a conducting channel

between the n + ohmic source and the drain contacts. At DC conditions, the depletion

regions and the neutral substrate provide isolation between devices fabricated on the

same substrate. A schematic view of the nchannel MOSFET is shown in Figure 2.10.

As described above for the MOS capacitor, inversion charge can be induced in the

channel by applying a suitable gate voltage relative to other terminals. The onset of

strong inversion is defined in terms of a threshold voltage VT being applied to the gate

electrode relative to the other terminals. In order to assure that the induced inversion

channel extends all the way from source to drain, it is essential that the MOSFET gate

structure either overlaps slightly or aligns with the edges of these contacts (the latter is

achieved by a selfaligned process). Selfalignment is preferable since it minimizes the

parasitic gatesource and gatedrain capacitance.

When a drainsource bias VDS is applied to an nchannel MOSFET in the abovethreshold

conducting state, electrons move in the channel inversion layer from source to drain. A

change in the gatesource voltage VGS alters the electron sheet density in the channel,

modulating the channel conductance and the device current. For VGS > VT in an nchannel

device, an application of a positive VDS gives a steady voltage increase from

source to drain along the channel that causes a corresponding reduction in the local gatechannel

bias VGX (here X signifies a position x within the channel). This reduction is

greatest near drain where VGX equals the gatedrain bias VGD.

Somewhat simplistically, we may say that when VGD = VT, the channel reaches threshold

at the drain and the density of inversion charge vanishes at this point. This is the socalled

pinchoff condition, which leads to a saturation of the drain current Ids. The

corresponding drainsourcevoltage, VDS = VSAT, is called the saturation voltage. Since

VGD = VGS – VDS, we find that VSAT = VGS – VT.

When VDS > VSAT, the pinchedoff region near drain expands only slightly in the

direction of the source, leaving the remaining inversion channel intact. The point of

transition between the two regions, x = xp, is characterized by XS ( p ) SAT V x » V , where

( ) XS p V x is the channel voltage relative to source at the transition point. Hence, the drain

current in saturation remains approximately constant, given by the voltage drop VSAT

across the part of the channel that remains in inversion. The voltage VDS – VSAT across

the pinchedoff region creates a strong electric field, which efficiently transports the

electrons from the strongly inverted region to the drain.

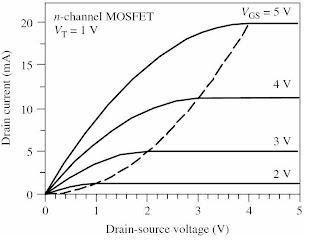

Typical currentvoltage characteristics of a longchannel MOSFET, where pinchoff is

the predominant saturation mechanism, are shown in the following figure.

However, with shorter MOSFET gate lengths, typically n the submicrometer range,

velocity saturation will occur in the channel near drain at lower VDS than that causing

pinchoff. This leads to more evenly spaced saturation characteristics than those shown in

this figure, more in agreement with those observed for modern devices. Also, phenomena

such as a finite channel conductance in saturation, a drain biasinduced shift in the

threshold voltage, and an increased subthreshold current are important consequences of

shorter gate lengths.

2.2.4 MOS Charge Control Model

2.2.4 MOS Charge Control Model

Well above threshold, the charge density of the mobile carriers in the inversion layer can

be calculated using the parallel plate charge control model of (2.28). This model gives an

adequate description for the strong inversion regime of the MOS capacitor, but fails for

applied voltages near and below threshold (i.e. in the weak inversion and depletion

regimes). Several expressions have been proposed for a unified charge control model

(UCCM) that covers all the regimes of operation, including the following:

where, a i c » c is approximately the insulator capacitance per unit area (with a small

correction for the finite vertical extent of the inversion channel), n0 = ns(V = VT) is the

density of minority carriers per unit area at threshold, and h is the socalled

subthreshold ideality factor, also known as the subthreshold swing parameter. The ideality factor

accounts for the subthreshold division of the applied voltage between the gate insulator

and the depletion layer, and the 1/h represents the fraction of this voltage that contributes

to the interface potential. A simplified analysis gives

This expression reproduces the correct limiting behaviour both in strong inversion and

the subthreshold regime, although it deviates slightly from (2.34) near threshold. The

various charge control expressions of the MOS capacitor are compared in the above

figure.

2.2.3 MOS Capacitance

2.2.3 MOS Capacitance

In a MOS capacitor, the metal contact and the neutral region in the doped semiconductor

substrate are separated by the insulator layer, the channel, and the depletion region.

Hence, the capacitance Cmos of the MOS structure can be represented as a series

connection of the insulator capacitance i i i C = S e d , where S is the area of the MOS

capacitor, and the capacitance of the active semiconductor layer Cs,

where Qs is the total charge per unit area in the semiconductor and y

s is the surface

potential. Using (2.9) to (2.12) for Qs and performing the differentiation , we obtain

here, s s Dp C = Se L 0 is the semiconductor capacitance at the flatband

condition (i.e., for

ys

=0) and LDp is the Debye length given by (2.11), equation (2.14) describes the

relationship between the surface and the applied bias.

The semiconductor capacitance can formally be represented as the sum of two

capacitancesa depletion layer capacitance, Cd and a free carrier capacitance Cfc. Cfc

together with a series resistance RGR describes the delay caused by thegeneration/

recombination mechanisms in the buildup and removal of inversion charge in

response to changes in the bias voltage. The depletion layer capacitance is given by

d s d C = Se / d

is the depletion layer width. In strong inversion, a change in the applied voltage will

primarily affect the minority carrier charge at the interface, owing to the strong

dependence of this charge on the surface potential. This means that the depletion width

reaches a maximum value with no significant further increase in the depletion charge.

This maximum depletion width ddT can be determined from (2.23) by applying the

threshold condition, y s= 2jb. the corresponding minimum value of the depletion

capacitance is

CdT = S es / ddT.

As indicated, the variation in the minority carrier charge at the interface comes from the

processes of generation and recombination mechanisms, with the creation and removal of

electronhole pairs. Once an electronhole pair is generated, the majority carrier (a hole in

ptype material and an electron in ntype material) is swept from the space charge region

into the substrate by the electric field of this region. The minority carrier is swept in the

opposite direction toward semiconductorinsulator interface. The variation in the minority

carrier charge in the semiconductorinsulator interface therefore proceeds at a rate limited

by the time constants associated with the generation/recombination processes. This finite

rate represents a delay, which may be represented electrically in terms of an RC product

consisting of the capacitance Cfc and the resistance RGR, as reflected in the equivalent

circuit of the MOS structure shown in figure 2.7. The capacitance Cfc becomes important

in the inversion regime, especially in strong inversion where the mobile charge is

important. The resistance Rs in the equivalent circuit is the series resistance of the neutral

semiconductor layer and the contacts.

The calculated dependence of Cmos on the applied voltage for different frequencies is

shown in figure 2.8. For applied voltages well below threshold, the device is in accumulation

and Cmos equals Ci. As the voltage approaches threshold, the semiconductor passes the

flatband condition where Cmos has the value CFB, and then enters the depletion and weak

inversion regimes where the depletion width increases and the capacitance value drops steadily

until it reaches the minimum value at threshold given by (2.27). The calculated curves clearly

demonstrate how the MOS capacitance in the strong inversion regime depends on the frequency, with a value of ¥ mos C at high frequencies to Ci at low frequencies.

We note that in a MOSFET, where the highly doped source and drain regions act as

reservoirs of minority carriers for the inversion layer, the time constant RGRCfc must be

19 substituted by a much smaller time constant corresponding to the time needed for

transporting carriers from these reservoirs in and out of the MOSFET gate area.Consequently,

highfrequency strong inversion MOSFET gatechannel CV characteristics will resemble the

zero frequency MOS characteristics.

2.2.2 Threshold Voltage

2.2.2 Threshold Voltage

The threshold voltage V=VT, corresponding to the onset of the strong inversion, is one of

the most important parameters characterizing metalinsulatorsemiconductor devices. As

discussed above, strong inversion occurs when the surface potential s y becomes equal to

2j b . For this surface potential, the charge of the free carriers induced at the insulator –

semiconductor interface is still small compared to the charge in the depletion layer, which

is given by

constant potential. Assuming that the inversion layer is grounded, VB biases the effective

junction between the inversion layer and the substrate, changing the amount of charge in

the depletion layer. In this case, the threshold voltage becomes

T FB b s a ( b B ) i V = V + 2j + 2e qN 2j - V c (2.18)

Note that the threshold voltage may also be affected by socalled fast surface states at the

semiconductoroxide interface and by fixed charges in the insulator layer. However, this

is not a significant concern with modern day fabrication technology.

As discussed above, the threshold voltage separates the subthreshold regime, where the

mobile carrier charge increases exponentially with increasing applied voltage, from the

abovethreshold regime, where the mobile carrier charge is linearly dependent on the

applied voltage.

2.2 The MOS Capacitor

constitutes the important gatechannelsubstrate structure of the MOSFET. The MOS

capacitor is a two terminal semiconductor device of practical interest in its own right. As

indicated in figure 2.2, it consists of a metal contact separated from the semiconductor

substrate. Almost universally, the MOS structure utilizes doped silicon as the substrate

and its native oxide, SiO2, as the insulator. In the siliconsilicon dioxide system, the

density of surface states at the oxidesemiconductor interface is very low compared to the

typical channel carrier density in a MOSFET. Also, the insulating quality of the oxide is

quite good.

We assume that the insulator layer has infinite resistance, preventing any charge carrier

transport across the dielectric layer when a bias voltage is applied between the metal and

semiconductor. Instead, the applied voltage will induce charges and counter charges in

the metal and in the interface layer of the semiconductor, similar to what is expected in

the metal plates of a conventional parallel plate capacitor. However, in the MOS

capacitor we may use the applied voltage to control the type of interface charge we

induce in the semiconductor – majority carriers, minority carriers and depletion region.

Indeed, the ability to induce and modulate a conducting sheet of minority careers at the

semiconductor – oxide interface is the basis of the operation of the MOSFET.

2.2.1 Interface Charge

The induced interface charge in the MOS capacitor is closely linked to the shape of the

electron energy bands of the semiconductor near the interface. At zero applied voltage,

the bending of the energy bands are ideally determined by the difference in the work

functions of the metal and the semiconductor. This band bending changes with the

applied bias and the bands become flat when we apply the socalled flatband voltage

given by

where Fm and FS are the work functions of the metal and the semiconductor,

respectively, XS is the electron affinity for the semiconductor, Ec is the energy of the

conduction band edge and EF is the Fermi level at zero applied voltage. The various

energies involved are indicated in figure 2.3, where we show typical band diagrams of

MOS capacitor at zero bias and with the voltage V=VFB applied to the metal contact

relative to the semiconductoroxide interface.

At stationary conditions, no net current flows in the direction perpendicular to the

interface owing to the very high resistance of the insulator layer. Hence, the Fermi level

will remain constant inside the semiconductor, independent of the biasing conditions.

However, between the semiconductor and the metal contact, the Fermi level is shifted by

EFM – EFS = qV (see Figure 2.3(b)). Hence, we have a quasiequilibrium

situation in which the semiconductor can be treated as if in thermal equilibrium.

A MOS structure with a ptype semiconductor will enter the accumulation regime of

operation when the voltage applied between the metal and the semiconductor is more

negative than the flatband voltage (VFB < 0 in Figure 2.3). In the opposite case, when

V > VFB, the semiconductoroxide interface first becomes depleted of holes and we enter

the socalled depletion regime.

By increasing the applied voltage, the band bending becomes so large that the energy

difference between the Fermi level and the bottom of the conduction band at the

insulatorsemiconductor interface becomes smaller than that between the Fermi level and

the top of the valance band. This is the case indicated for V = 0V in Figure 2.3 (a).

Carrier statistics tells us that the electron concentration then will exceed the hole

concentration near the interface and we enter the inversion regime. At still larger applied

voltage, we finally arrive at a significant conducting sheet of inversion charge at the

interface.

The symbol y is used to signify the potential in the semiconductor measured relative to

the potential at a position x deep inside the semiconductor. To note that y becomes

positive when the bands bend down, as in the example of a ptype semiconductor shown

in Figure 2.4.

from equilibrium statistics, we find that the intrinsic Fermi level Ei in the bulk

corresponds to an energy separation qjb from the actual Fermi level EF of the doped

semiconductor,

where Vth is the thermal voltage, Na is the shallow acceptor density in the ptype

semiconductor and ni is the intrinsic carrier density of silicon. According to the usual

definition, strong inversion is reached when the total band bending equals 2qjb,

corresponding to the surface potential y s = 2jb. Values of the surface potential such that

0 < y s < 2jb correspond to the depletion and the weak inversion regimes, y

s = 0 is the flatband condition, and y s < 0 corresponds to the accumulation mode.

Chapter 2::MOS Device Physics and Operations

MOS Device Physics and Operations

2.1 Introduction

A field effect transistor (FET) operates as a conducting semiconductor channel with two

ohmic contacts the source and the drain – where the number of charge carriers in the

channel is controlled by a third contact – the gate. In the vertical direction, the gatechannel

substrate structure (gate junction) can be regarded as an orthogonal twoterminal device,

which is either a MOS structure or a reversebiased rectifying device that controls

the mobile charge in the channel by capacitive coupling (field effect). Examples of FETs

based on these principles are MetalOxideSemiconductor FET (MOSFET), junction FET

(JFET), metalsemiconductor FET (MESFET), and heterostructure FET (HFETs). In all

cases, the stationary gatechannel impedance is very large at normal operating conditions.

The basic FET structure is shown schematically in figure 2.1.

The most important FET is the MOSFET. In a silicon MOSFET, the gate contact is

separated from the channel by an insulating silicon dioxide (SiO2) layer. The charge

carriers of the conducting channel constitute an inversion charge, that is, electrons in the

case of a ptype substrate (nchannel device) or holes in the case of an ntype

substrate(pchannel device), induced in the semiconductor at the siliconinsulator

interface by the voltage applied to the gate electrode. The electrons enter and exit the

channel at n + sourceand drain contacts in the case of an nchannelMOSFET, and at

p+ contacts in the case of a pchannel MOSFET.

MOSFETs are used both as discrete devices and as active elements in digital and analog

monolithic integrated circuits (ICs). In past decade, the device feature size of such

circuits has been scaled down into the deep submicrometer range. Presently, the 0.13mm

technology node for complementary MOSFET (CMOS) is used very large scale Ics.

(VLSIs) and, within a few years, sub0.1mm technology will be available, with a

commensurate increase in speed and in integration scale. Hundreds of millions of

transistors on a single chip are used in microprocessors and in memory ICs today.

CMOS technology combines both nchannel and pchannel MOSFETs to provide very

low power consumption along with high speed. New silicononinsulator (SOI)technology

may help achieve threedimensional integration, that is, packing of devices

into many layers with a dramatic increase in integration density. New improved device

structures and the combination of bipolar and field effect technologies (BiCMOS) may

lead to further advances, yet unforeseen. One of the rapidly growing areas of CMOS is in

analog circuits, spanning a variety of applications from audio circuits operating at the

kilohertz (kHz) range to modern wireless applications operating at gigahertz (GHz)

frequencies.

Introduction

1.1 History

Metal Oxide Semiconductor Field Effect Transistor(MOSFET) is used in a vast

mannerin VLSI design for high speed performance, safe operating area, unipolarity and

easiness to be used in parallel. For the study of MOSFET characteristics and operations

models have been proposed. All these models have their own assumptions and

predictions. Due to scaling of MOSFETs, it has become very significant to consider the

effect of generated traps in SiSiO2 junction. The interface states although are not of

significance in case of thicker gate oxides but study of devices with tunneling oxide

thickness (~ 2 nm) shows that these almost negligible states have remarkable impact on

the drive current. As the oxide thickness is reduced these interfacetrapped charges

become significant gradually. In earlier times, gate oxide thickness was so large that this

phenomenon was not noticeable, but introduction of nanotechnology puts a barrier in

determining the nature of the MOSFETs with ultra thin oxides. As a result, now a day it

is a matter of importance to consider the interface states during MOS operation.

1.2 A glimpse of previous works on interface trapped charges

A theoretical treatment on the process of hotelectron

emission from silicon into SiO2

was carried out by Ning [1]. He considered avalanche and nonavalanche injection

mechanism to calculate emission probability of the carriers at SiSiO2

interface. Yambae

and Miura [2] observed experimentally the flat band voltage shift due to the generation of

interface states because of electron trapping in the SiO2 film. They suggested that the

2 interface states, where electrons can be trapped, are generated due to the collisions of

electrons at the SiSiO2interface.Khosru and others [3] observed that holes are created

by ionizing radiation that produces new electronic states at the SiSiO2 interface resulting

in the formation of interface traps.

They also found a threshold voltage shift due to the trapping of carriers inside the SiO2

layer.

In a recent approach, KueiShan Wen and others [4] showed that the generated electron

traps at the SiSiO2interface enhance the degradation of MOSFET characteristics. To

determine the interface trapped charges in a SiSiO2 interface Guido Goreseneken and

others [5] used the charge pumping method introduced by Brugler and Jespers [6] and

represented a very keen analysis of energy distribution of interface trapped charges.

1.3 Outline of the report In this report, we represented our work in a few chapters.

These chapters are as follows:· Chapter 2: In this chapter, the physics and operation of

MOS devices are studied in detail. Especially, the theory of MOS capacitor is

presented. The dependency of MOS capacitance on frequency and applied voltage is also

showed. A brief description on the MOSFET operation is discussed in the end.

· Chapter 3: The physical alphapower law MOSFET model is explained in detail in this

chapter. The expressions of the model along with compact mathematical analyses and plots

of IDS vs. VGS curves and IDS vs. VDS curves for two different devices (3.5 nm oxide

and 2.2 nm oxide)are presented. Discussing briefly about the plots, an outline of the

operation of the ultrathin oxide MOSFETs are understandable. In the end 3portion of this

chapter an analysis of the subthreshold slope of thedevices is presented.

Chapter 4: This chapter deals with the development of the physical

alphapower law MOSFET model. The incorporation of depletioncapacitance (Cd) and

interface trapped charge capacitance (Cit) shows an amount of difference in the IDS vs. VGS

and IDS vs. VDS curves for both the devices. Respective plots in this purpose are included.

· Chapter 5: A detailed description on the location and properties of the interface states in a

MOS device is discussed here. Also, it includes a glimpse in the Si – SiO2 interface.

· Chapter 6: This chapter deals with two types of determination process

of interface trapped charges: 1) The Charge Pumping Method or CP Method, 2) The Capac-

itanceVoltage Method or CV Method. Later in this chapter an analytical study and comparis-

on between this two methods is presented.

Subscribe to:

Posts (Atom)